# **General Description**

The SY7T625 is the host side device of an isolated metering chipset for single-phase or poly-phase electricity metering applications. Featuring Silergy's proprietary Teridian power measurement technology, up to four isolated analog front end (AFE) devices are supported, each utilizing an independent, robust capacitively coupled digital interface. Each AFE supports two ADC channels (voltage and current) to form a highly accurate and fully isolated shuntbased meter.

A powerful 24-bit Compute Engine and math accelerators implement the core requirements of high accuracy metering. Code images that cover most requirements of revenue metering are provided by Silergy. These images can be pre-loaded into the flash memory of the SY7T625 by ordering option, programmed at production, and can be updated in the field, if necessary. The flash memory is also used to store calibration coefficients generated during meter calibration and configuration.

Designed as a completely autonomous metrology processor, a set of pre-processed metrology outputs can be obtained by reading registers via the SPI interface. Likewise, system parameters, such as the desired meter constant (Kh), calibration coefficients, sag threshold, and other parameters can be written to RAM by the host.

A sophisticated onboard clock management system provides an internal clock source and automatically utilizes an optional external crystal if the highest accuracy timing is desired. An integrated hardware Watchdog Timer (WDT) is also included.

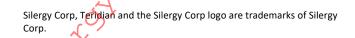

The example schematic illustrates an application of four SY7M007 isolated AFEs connected to voltage and current sensors for each phase. Scaled voltages from the sensors are digitized, and the data stream of measurement data is coupled to the SY7T625 with discrete or PCB capacitors.

# Features

- Isolated AFE interface supports up to four compatible Silergy remote ADCs (up to 8 analog inputs)

- Powerful 24-bit Compute Engine with 20MHz clock frequency, supported by accelerators for multiply, divide, and square root operations

- Factory-programmed or field programmable with Silergy provided firmware images

5x5mm 32-pin QFN package

- SPI host interface, up to 10MHz

- Two pulse outputs and 10 additional digital I/O pins

- 20MHz crystal (or external clock) interface for precision timing reference

# Applications

Poly-phase smart meters

DS\_SY7T625 Rev 0.9 © 2020 Silergy Corp

Silergy Corp. Confidential- Prepared for Customer Use Only

# **Ordering Information**

| Orderin   | g Numb                                         | ber                                                                    | Pre-programmed Firm                                                                                                                                                                                                                      | vare                                                     |                                                                                  | Package Top Ma                                                                                                                                                                                                                                                                                        | ırk |  |

|-----------|------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| SY7T625   | <br>БТ                                         |                                                                        | internal flash must be erased and Sile                                                                                                                                                                                                   | rgy-pi                                                   | rovided firmwa                                                                   | CVTTC2                                                                                                                                                                                                                                                                                                | 5   |  |

|           |                                                |                                                                        | e installed by the OEM)                                                                                                                                                                                                                  | Bells Compliant and BRY                                  |                                                                                  |                                                                                                                                                                                                                                                                                                       |     |  |

| SY7T625   |                                                |                                                                        | I flash contains standard meter firmw                                                                                                                                                                                                    |                                                          |                                                                                  | Halogen Free                                                                                                                                                                                                                                                                                          |     |  |

| RR=Die re | evision c                                      | ode, YY=yea                                                            | r (2 digits) of assembly, WW=work we                                                                                                                                                                                                     | eek of                                                   | assembly, Z= l                                                                   | ot code                                                                                                                                                                                                                                                                                               |     |  |

|           |                                                |                                                                        | Pin                                                                                                                                                                                                                                      | out                                                      | Ŷ                                                                                | ot code                                                                                                                                                                                                                                                                                               |     |  |

|           |                                                |                                                                        | N C N<br>N C N<br>N C N                                                                                                                                                                                                                  | INBN                                                     | AP                                                                               | $O^{\mathbf{Y}}$                                                                                                                                                                                                                                                                                      |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          |                                                          |                                                                                  | A A A A A A A A A A A A A A A A A A A                                                                                                                                                                                                                                                                 |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          | 28 27                                                    | <sup>26</sup> <sup>25</sup> <sup>24</sup> V3P3                                   | A                                                                                                                                                                                                                                                                                                     |     |  |

|           |                                                |                                                                        | DIO15 ] 2<br>DIO8 ] 3                                                                                                                                                                                                                    | 4                                                        | <sup>23</sup> [ RES                                                              |                                                                                                                                                                                                                                                                                                       |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          | Y                                                        | 22 0109<br>21 0101                                                               |                                                                                                                                                                                                                                                                                                       |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          | /iew                                                     |                                                                                  |                                                                                                                                                                                                                                                                                                       |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          |                                                          | 19 <b>DIO1</b>                                                                   | 1                                                                                                                                                                                                                                                                                                     |     |  |

|           |                                                |                                                                        | DIO13 ] 7<br>DIO5 ] 9                                                                                                                                                                                                                    |                                                          |                                                                                  |                                                                                                                                                                                                                                                                                                       |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          | 13 14                                                    |                                                                                  |                                                                                                                                                                                                                                                                                                       |     |  |

|           |                                                |                                                                        | DIO4                                                                                                                                                                                                                                     |                                                          | GND<br>DIO3                                                                      |                                                                                                                                                                                                                                                                                                       |     |  |

|           |                                                |                                                                        |                                                                                                                                                                                                                                          | Š 0                                                      | 0                                                                                |                                                                                                                                                                                                                                                                                                       |     |  |

|           | Pin                                            | Signal                                                                 | Function                                                                                                                                                                                                                                 | Pin                                                      | Signal                                                                           | Function                                                                                                                                                                                                                                                                                              |     |  |

|           | 1                                              | GNDA                                                                   | Analog GND                                                                                                                                                                                                                               | 17                                                       | DIO2                                                                             | SPI MOSI (SDI)                                                                                                                                                                                                                                                                                        |     |  |

|           | 2                                              | DIO15                                                                  | Digital I/O                                                                                                                                                                                                                              | 18                                                       | DIO1                                                                             | SPI SCK                                                                                                                                                                                                                                                                                               |     |  |

|           | 3                                              | DIO8                                                                   | Digital I/O                                                                                                                                                                                                                              | 19                                                       | DIO11                                                                            | Digital I/O                                                                                                                                                                                                                                                                                           |     |  |

|           | 4                                              | DIO7                                                                   |                                                                                                                                                                                                                                          |                                                          |                                                                                  | 8                                                                                                                                                                                                                                                                                                     |     |  |

|           |                                                |                                                                        | Digital I/O                                                                                                                                                                                                                              | 20                                                       | DIOO                                                                             | Digital I/O                                                                                                                                                                                                                                                                                           |     |  |

|           | 5                                              | DI014                                                                  | Digital I/O                                                                                                                                                                                                                              | 20<br>21                                                 | DIO0<br>DIO10                                                                    |                                                                                                                                                                                                                                                                                                       |     |  |

|           | 5                                              | N. *                                                                   |                                                                                                                                                                                                                                          |                                                          |                                                                                  | Digital I/O                                                                                                                                                                                                                                                                                           |     |  |

|           |                                                | DI014                                                                  | Digital I/O                                                                                                                                                                                                                              | 21                                                       | DIO10                                                                            | Digital I/O<br>Digital I/O                                                                                                                                                                                                                                                                            |     |  |

|           |                                                | DI014<br>DI06                                                          | Digital I/O                                                                                                                                                                                                                              | 21<br>22                                                 | DIO10<br>DIO9                                                                    | Digital I/O<br>Digital I/O<br>Digital I/O                                                                                                                                                                                                                                                             |     |  |

|           | 6                                              | DIO14<br>DIO6<br>DIO13                                                 | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O                                                                                                                                                                             | 21<br>22<br>23                                           | DIO10<br>DIO9<br>RESETB                                                          | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)                                                                                                                                                                                                                                 |     |  |

|           | 6<br>7<br>8                                    | DI014<br>DI06<br>DI013<br>DI05                                         | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O<br>SPI Select SSB                                                                                                                                                           | 21<br>22<br>23<br>24                                     | DIO10<br>DIO9<br>RESETB<br>V3P3A                                                 | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)                                                                                                                                                                                                       |     |  |

|           | 6<br>7<br>8<br>9                               | DI014<br>DI06<br>DI013<br>DI05<br>DI04                                 | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O<br>SPI Select SSB<br>Digital I/O or VARh pulse output                                                                                                                       | 21<br>22<br>23<br>24<br>25                               | DIO10<br>DIO9<br>RESETB<br>V3P3A<br>INAP                                         | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)<br>Remote Interface A (positive)                                                                                                                                                                      |     |  |

|           | 6<br>7<br>8<br>9<br>10                         | DIO14<br>DIO6<br>DIO13<br>DIO5<br>DIO4<br>DIO12                        | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O<br>SPI Select SSB<br>Digital I/O or VARh pulse output<br>Digital I/O                                                                                                        | 21<br>22<br>23<br>24<br>25<br>26                         | DIO10<br>DIO9<br>RESETB<br>V3P3A<br>INAP<br>INAN                                 | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)<br>Remote Interface A (positive)<br>Remote Interface A (negative)                                                                                                                                     |     |  |

|           | 6<br>7<br>8<br>9<br>10<br>11                   | DIO14<br>DIO6<br>DIO13<br>DIO5<br>DIO4<br>V3P3D                        | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O<br>SPI Select SSB<br>Digital I/O or VARh pulse output<br>Digital I/O<br>3.3VDC Supply (Digital)                                                                             | 21<br>22<br>23<br>24<br>25<br>26<br>27                   | DIO10<br>DIO9<br>RESETB<br>V3P3A<br>INAP<br>INAN<br>INBP                         | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)<br>Remote Interface A (positive)<br>Remote Interface A (negative)<br>Remote Interface B (positive)                                                                                                    |     |  |

|           | 6<br>7<br>8<br>9<br>10<br>11<br>12             | DIO14<br>DIO6<br>DIO13<br>DIO5<br>DIO4<br>V3P3D<br>XIN                 | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O<br>SPI Select SSB<br>Digital I/O or VARh pulse output<br>Digital I/O<br>3.3VDC Supply (Digital)<br>Crystal Oscillator Input                                                 | 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28             | DIO10<br>DIO9<br>RESETB<br>V3P3A<br>INAP<br>INAN<br>INBP<br>INBN                 | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)<br>Remote Interface A (positive)<br>Remote Interface A (negative)<br>Remote Interface B (positive)<br>Remote Interface B (negative)                                                                   |     |  |

| .~        | 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13       | DIO14<br>DIO6<br>DIO13<br>DIO5<br>DIO4<br>V3P3D<br>XIN<br>XOUT         | Digital I/O<br>Digital I/O of Wh pulse output<br>Digital I/O of Wh pulse output<br>SPI Select SSB<br>Digital I/O or VARh pulse output<br>Digital I/O<br>3.3VDC Supply (Digital)<br>Crystal Oscillator Input<br>Crystal Oscillator Output | 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29       | DIO10<br>DIO9<br>RESETB<br>V3P3A<br>INAP<br>INAN<br>INBP<br>INBN<br>INBN<br>INCP | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)<br>Remote Interface A (positive)<br>Remote Interface A (negative)<br>Remote Interface B (positive)<br>Remote Interface B (positive)<br>Remote Interface C (positive)                                  |     |  |

|           | 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | DIO14<br>DIO6<br>DIO13<br>DIO5<br>DIO4<br>V3P3D<br>XIN<br>XOUT<br>GNDD | Digital I/O<br>Digital I/O<br>Digital I/O<br>SPI Select SSB<br>Digital I/O or VARh pulse output<br>Digital I/O<br>3.3VDC Supply (Digital)<br>Crystal Oscillator Input<br>Crystal Oscillator Output<br>Ground (Digital)                   | 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 | DIO10<br>DIO9<br>RESETB<br>V3P3A<br>INAP<br>INAN<br>INBP<br>INBN<br>INCP<br>INCN | Digital I/O<br>Digital I/O<br>Digital I/O<br>Reset Input (Active Low)<br>3.3VDC Supply (Analog)<br>Remote Interface A (positive)<br>Remote Interface A (negative)<br>Remote Interface B (positive)<br>Remote Interface B (negative)<br>Remote Interface C (positive)<br>Remote Interface C (negative) |     |  |

2

### **Hardware Description** 1.

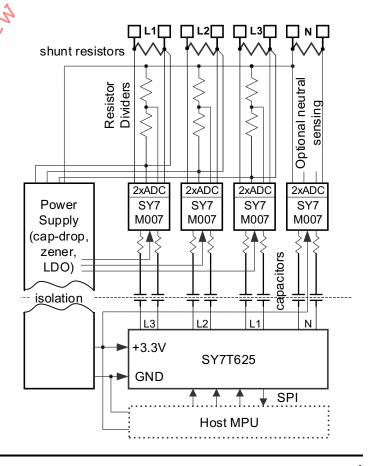

The SY7T625 integrates all the functional hardware blocks required for solid-state electricity metering. Only a few external resistors and capacitors are required. Included on the device are:

- Remote (Rx) interface for capacitive coupling to remote ADCs .

- Two FIRs per remote

- 24-bit Compute Engine with RAM and Flash memory

- Digital I/O with SPI peripheral interface and low jitter pulse outputs

- Oscillator and clock management logic

- Integrated power-on reset and watchdog timer

## 1.2 Clock Management, Power-On Reset, and Watchdog Timer

### **Clock Management**

The SY7T625 integrates an RC oscillator for fast start-up and includes the circuitry to handle an external crystal or ceramic resonator. The clock management unit of the SY7T625 automatically handles the clock sources logic and distributes the clock to the rest of the device.

Upon reset or power-on, the SY7T625 starts-up on the internal RC oscillator. After 1024 clock cycles of the internal RC oscillator, the clock management logic will switch to the external 20MHz clock (if available), allowing the external crystal an adequate start-up time. If no valid external clock is detected, the clock management logic will keep clocking the device using the internal RC oscillator. If the device is normally clocked using the external 20MHz crystal, the clock management logic continuously monitors the status of the clock. The clock management logic of the SY7T625 will automatically switch to the internal oscillator in the event of a failure of the external oscillator (or crystal not mounted).

The internal RC oscillator is trimmed and provides an accurate clock source, however for metering applications requiring highest accuracy of the time-based measurements (i.e. line frequency, energy, etc.), the use of an external crystal is required. Alternatively, an external clock signal can be utilized instead of the crystal. In this case, the external clock should be connected to the XOUT pin while the XIN pin should be connected to GNDD.

### Power-On Reset (POR)

An on-chip Power-On Reset (POR) block monitors the supply voltage (V3P3D) and initializes the internal digital circuitry at power-on. Once V3P3D is above the minimum operating threshold, the POR circuit triggers and initiates a reset sequence. It will also issue a reset to the digital circuitry if the supply voltage falls below the minimum operating level.

### External Reset Pin (RESETB Pin)

In addition to the internal reset sources, a reset can be forced by applying a low level to the RESETB pin for a duration of > Tspike (MAX) (see the Transient Spike Tolerance specification in the Electrical Characteristics section of this document).

If the RESETB pin is pulled low, all digital activities in the device stop, except the clock management circuitry and oscillators, which continue to run.

### Watchdog Timer (WDT)

A Watchdog Timer (WDT) block detects any software processing errors. The embedded firmware periodically refreshes the freerunning watchdog timer to prevent it from timing out. If the WDT times out, it is an indication that software is no longer being executed in the intended sequence; thus, a system reset is initiated.

# 1.3 Isolated (Remote ADC) Interface

The SY7T625 communicates with one or more remote ADCs (e.g. the SY7M007 dual-channel remote ADC) via capacitive isolation. The communication protocol is proprietary. Below are a few characteristics of the data link:

- Data are sent exclusively from the remote ADCs to the SY7T625 host. Neither commands nor data are sent in the opposite direction.

- Differential signaling is used for best rejection of common-mode noise. Every remote drives two signals, RCP and RCN with approximately 3.2V peak amplitudes. Depending on the value of the coupling capacitor, the peak voltage received at the SY7T625 can be as low as 50mV (66mV typical with 0.2pF PCB capacitors interacting with 10pF trace/pin capacitance in the SY7T625).

- Manchester encoding is used to ensure that there is no DC component to the signal and that the clock can be recovered by the \$777625.

- The half-bit bit-time is 10MHz, or 100ns. Each full bit occupies 200ns.

- The ADC sample data generated by the sigma-delta comparator stage in the remote ADCs is transmitted in the form of a bit stream to the host and decimated via FIR filters in the SY7T625.

ADC sample data and auxiliary data such as die temperature, supply voltage, trim information, etc. are sent in 'data frames' of 7 bits to the SY7T625 host. Each frame contains 4 bits for synchronization, one bit each for the current and the voltage samples, and one side-channel bit. Each data frame occupies 1.4µs.

Δ

- The ADC sample data are transmitted to the SY7T625 sequentially and matched to factory programmed periods for chopping of the bandgap reference. Factory-programmable settings of the FIR filters in the SY7T625 allow various combinations of effective sample frequency and resolution.

- Timing for a typical application assumes that 170 bits are collected for one complete 'multiplexer frame', resulting in a mux frame time of 170 \* 1.4µs = 238µs (4201.68Hz).

- The polarity of the signals at the INAP/INAN, INBP/INBN, etc. pins of the SY7T625 can be swapped to accommodate signal routing on the PCB.

The design of the remote communication link is optimized for two distinct capacitance values. The capacitors can be implemented in two ways:

- 1) Discrete capacitors, 100pF, in series with  $200k\Omega$  resistors

- 2) PCB capacitors, 0.2pF (4mm x 4mm and 2mm x 2mm copper plates on opposing sides of a 1.6mm thick PCB), in series with 2kΩ resistors

A configuration bit in the SY7T625 matches the remote interface to the selected capacitor configuration. Minor differences in the capacitance values and the capacitive load from traces and input pins of the SY7T625 for the two capacitors for each remote link can be balanced using bit fields that are accessible through the SPI interface (see the CE Code Reference Manual for details). Common-mode values read from the remote pin pairs are accessible via one register per remote channel.

# 1.4 Compute Engine

The Compute Engine is a dedicated 24-bit DSP that performs the signal processing necessary to accurately measure energy. The Compute Engine is a programmable core for which Silergy typically provides binary code modules used to perform energy computations. The CE calculations and processes may include:

- Multiplication of each current sample with its associated voltage sample to obtain the energy per sample (when multiplied with the constant sample time)

- 90° phase shifter (for VAR calculations)

- Pulse generation

- Measurement of the pout signal frequency (for frequency and phase information)

- Monitoring of the input signal amplitude (for sag detection)

- Scaling of the processed samples based on calibration coefficients

- Scaling of samples based on temperature compensation information

- Extraction, suppression or filtering of harmonics for special functions

- Variable gain compensation

- Variable phase compensation

# 1.5 Flash and RAM

The SY7T625 includes on-chip flash memory for storing program code, coefficients, calibration data, and configuration settings. The SY7T625 also includes on chip RAM which is used to store the values of input and output registers and utilized by the firmware for its operations.

# 1.6 Digital I/O

The SY7T625 features general-purpose digital I/O. The digital I/O are either managed directly by the user, by the embedded firmware, or multiplexed with the serial communication interfaces. The following table summarizes the multiplexing and pin assignment on the SY7T625.

| Pin | Hardware                          | Pin                      | Pin                                                                                                                                                 | Hardware                                                                                                                                                                                                                        |

|-----|-----------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #   | Peripheral                        | Name                     | #                                                                                                                                                   | O Peripheral 🔗                                                                                                                                                                                                                  |

| 2   |                                   | DIO7                     | 4 🤇                                                                                                                                                 |                                                                                                                                                                                                                                 |

| 5   |                                   | DIO6                     | 6                                                                                                                                                   | W Pulse                                                                                                                                                                                                                         |

| 7   |                                   | DIO5                     | 8                                                                                                                                                   | SSB                                                                                                                                                                                                                             |

| 10  |                                   | DIO4                     | 9                                                                                                                                                   | V Pulse                                                                                                                                                                                                                         |

| 19  |                                   | DIO3                     | 16                                                                                                                                                  | MISO                                                                                                                                                                                                                            |

| 21  |                                   | D1O2                     | 17                                                                                                                                                  | MOSI                                                                                                                                                                                                                            |

| 22  |                                   | 0101                     | 18                                                                                                                                                  | SCK                                                                                                                                                                                                                             |

| 3   | 5                                 | DIOO                     | 20                                                                                                                                                  | *                                                                                                                                                                                                                               |

|     | #   2   5   7   10   19   21   22 | #     Peripheral       2 | #     Peripheral     Name       2     DIO7       5     DIO6       7     DIO5       10     DIO3       21     DIO2       22     DIO1       3     DIO0 | #     Peripheral     Name     #       2     DIO7     4       5     DIO6     6       7     DIO5     8       10     DIO4     9       19     DIO3     16       21     DIO2     17       22     DIO1     18       3     DIO0     20 |

# 1.7 Serial Peripheral Interface (SPI)

SPI transactions work in two selectable modes:

- Native SY7T625 SPI operation mode (operation up to 1MHz)

- MAX71020-style SPI operation mode (operation up to 10MHz)

The code image provided by Silergy determines the SPI operation mode. In MAX71020-style SPI operation mode, SPI transactions are configured to provide immunity to electrical noise through redundancy in the command segment and error checking in the data field. The SY7T625 SPI transaction is exactly 64 bits (none of the fields are optional).

- Transactions of any other length are rejected and if an error is detected during the address or direction phase, no action is taken

- If extra clocks are provided at the end during a read, all zero is output and the status continues to be updated, signaling an error.

- If extra clocks are provided at the end during a write, the write is aborted, and the status is updated to signal an error.

- The status byte indicates the status of the previous SPI transaction except for the status byte parity.

- Access to the entire address range is allowed, unless Safe Mode is selected, which restricts access to the first 256 RAM locations (0x00 to 0xFF).

### 1.7.1 Reset Command

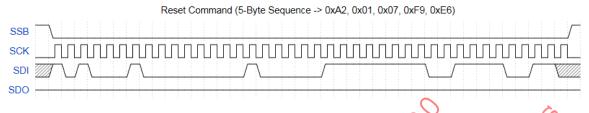

The reset command works identical for both SY7T625-style and MAX71020-style SPI modes. It is a 5-byte sequence (0xA2, 0x01, 0x07, 0xF9, 0xE6) issued by the host SPI master. The last bit of this 5-byte sequence is a don't-care bit.

|                |    | A |

|----------------|----|---|

|                | 2  |   |

| ~              | Ø  |   |

| $\sim$         | ,Y |   |

| $\mathcal{S}'$ |    |   |

| Byte Number | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 1           | 1     | 0     | 1     | 0     | 0     | 0     | 1     | 0     |

| 2           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

| 3           | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

| 4           | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 1     |

| 5           | 1     | 1     | 1     | 0     | 0     | 1     | 1     | х     |

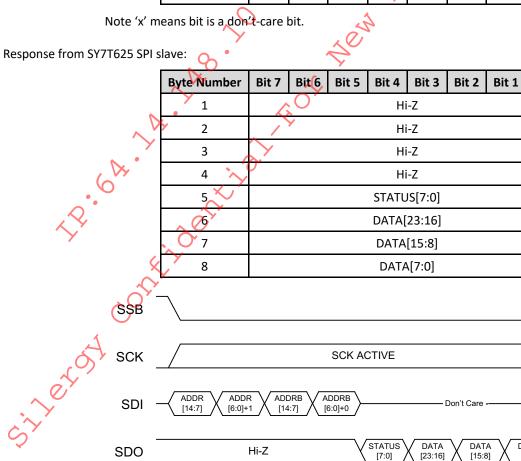

### 1.7.2 Single-Word SPI Reads

The read command from the host SPI master uses the target address (ADDR) and the inverted target address (ADDRB) for added security:

| Byte Number | Bit 7 | Bit 6       | Bit 5 | Bit 4 ( | Bit 3 | Bit 2  | Bit 1 | Bit 0 |  |

|-------------|-------|-------------|-------|---------|-------|--------|-------|-------|--|

| 1           |       | ADDR[14:7]  |       |         |       |        |       |       |  |

| 2           |       |             | А     | DDR[6:( | D]    |        |       | 1     |  |

| 3           |       | ADDRB[14:7] |       |         |       |        |       |       |  |

| 4           |       |             |       | DDRB[6: | 0]    | ý<br>C |       | 0     |  |

| 5           | х     | x           | ×     | х       | x     | x      | х     | х     |  |

| 6           | х     | ×           | х     | х       | ×     | х      | х     | х     |  |

| 7           | x     | x           | х     | x       | ×x    | х      | х     | х     |  |

| 8           | ×     | х           | х     | ×       | х     | х      | х     | х     |  |

DS\_SY7T625 Rev 0.9 © 2020 Silergy Corp

Silergy Corp. Confidential- Prepared for Customer Use Only

7

Bit 0

DATA

[7:0]

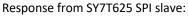

### 1.7.3 Single Word SPI Write

Write command from host SPI master (ADDR = target address, ADDRB = target address with bits reversed):

| te Number   Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1    | Bit 0 |

|-------------------|-------|-------|--------|---------|-------|----------|-------|

| 1                 |       |       | ADDR   | [14:7]  | C     |          | -     |

| 2                 |       | А     | DDR[6: | 0]      | 0     | <u>ک</u> | 0     |

| 3                 |       |       | ADDR   | 3[14:7] | 0'    |          |       |

| 4                 |       | A     | DDRB[6 | :0]     | V     |          | 1     |

| 5 x               | х     | х     | x      | X       | х     | х        | X     |

| 6                 |       |       | DATA[  | 23:16]  |       | 2        |       |

| 7                 |       |       | DATA   | [15:8]  |       | 0        |       |

| 8                 |       | ~     |        | A[7:0]  | ~     | Y        |       |

Note 'x' means that the bit is a don't-care bit

DS\_SY7T625 Rev 0.9 © 2020 Silergy Corp

### 1.7.4 Status Byte

Even parity is used for both data and status parity.

| Bit<br>7 | Name                                  | Description                                                           |

|----------|---------------------------------------|-----------------------------------------------------------------------|

| ,        | Status Parity                         | Parity of the status byte, STATUS [7:0] ('0' or '1' could be correct) |

| 6        | FIFO Overrun                          | SPI FIFO overrun error ('1' signifies error)                          |

| 5        | FIFO Underrun                         | SPI FIFO underrun error ('1' signifies error)                         |

| 4        | Data Parity                           | Parity of the data word, DATA [23:0] ('0' or '1' could be correct)    |

| 3        | Setting Mismatch                      | Address or direction mismatch error ('1' signifies error)             |

| 2        | (Reserved)                            | o'                                                                    |

| 1        | Bad Clock Count                       | Bit count not equal to 64 error ('1' signifies error)                 |

| 0        | Bad Address                           | Address out of bounds, when in SPI Safe Mode                          |

| J.P. Ch  | A A A A A A A A A A A A A A A A A A A | Date forke                                                            |

# 2 Electrical Specifications

### 2.1 Absolute Maximum Ratings (1)

| Supplies and Ground Pins:                                                                            |                                           |

|------------------------------------------------------------------------------------------------------|-------------------------------------------|

| V3P3D, V3P3A                                                                                         | -0.5V to 3.8V                             |

| GNDD, GNDA                                                                                           | -0.5V to +0.5V 🏷                          |

| Crystal Pins:                                                                                        |                                           |

| XIN, XOUT                                                                                            | -10mA to +10mA<br>-0.5V to 3:0V           |

| Digital Pins:                                                                                        | ~~<br>~                                   |

| DIO15, DIO14, DIO13, DIO12, DIO11, DIO10, DIO9, DIO8, DIO7, DIO6, DIO5, DIO4, DIO3, DIO2, DIO1, DIO0 | -10mA to +10mA<br>-0.5V to (V3P3D + 0.5V) |

| Receiver Input Pins:                                                                                 |                                           |

| INAN, INAP, INBN, INBP, INCN, INCP, INDN, INDP                                                       | -10mA to +10mA<br>-0.5V to (V3P3A + 0.5V) |

| Temperatures:                                                                                        |                                           |

| Operating Junction Temperature (peak, 100ms)                                                         | +140°C                                    |

| Operating Junction Temperature (continuous)                                                          | +125°C                                    |

| Storage Temperature                                                                                  | -45°C to +165°C                           |

| Soldering Temperature (10-second duration)                                                           | +250°C                                    |

| ESD Stress on All Pins                                                                               | ±2kV                                      |

# 2.2 Recommended Operating Conditions (2)

| Parameter                  | Condition        | Min | Тур | Max | Unit |

|----------------------------|------------------|-----|-----|-----|------|

| 3.3V Supply Voltage (V3P3) | Normal Operation | 3.0 | 3.3 | 3.6 | V    |

| Operating Temperature      |                  | -40 | -   | +85 | ₀C   |

# 2.3 Recommended External Components

| Name           | From  | То   | Function                                                                                                                             | Value    | Unit |

|----------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------|----------|------|

| C <sub>D</sub> | V3P3D | GNDD | Bypass capacitor for V3P3D                                                                                                           | 0.1±20%  | μF   |

| C <sub>A</sub> | V3P3A | GNDA | Bypass capacitor for V3P3A                                                                                                           | ≥1.0±30% | μF   |

| XTAL           | XIN   | XOUT | 20MHz crystal                                                                                                                        | 20.000   | MHz  |

| CXS            | XIN   | GNDD | Load capacitor values for crystal depend on crystal specifi-                                                                         | 20 ±10%  | pF   |

| CXL            | хоит  | GNDD | cations and board parasitics. Nominal values are based<br>on 4pF board capacitance and include an allowance for<br>chip capacitance. | 20 ±10%  | pF   |

|                |       |      |                                                                                                                                      |          |      |

## 2.4 Performance Specifications (3)

Note that production tests are performed at room temperature.

### 2.4.1 Input Logic Levels (Digital Pins)

| Parameter                                         | Condition              | Min                                     | Тур | Max             | Unit |

|---------------------------------------------------|------------------------|-----------------------------------------|-----|-----------------|------|

| Digital high-level input voltage, V <sub>IH</sub> |                        | 0.65*<br>V3P3D                          | -   | - 0             | V    |

| Digital low-level input voltage, V <sub>IL</sub>  | C                      | ×0-                                     | -   | 0.35 *<br>V3P3D | V    |

| Hysteresis                                        | ر<br>ا                 | 0.1 *<br>V3P3D                          |     | - 7             | V    |

| Input Pull-Up Resistor R <sub>PUP</sub>           |                        | 20                                      | 0   | 100             | kΩ   |

| Input High Current I <sub>IH</sub>                | Input Pull-Up Resistor | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | _   | +1              | μΑ   |

| Input Low Current I <sub>IL</sub>                 | Disabled               |                                         | _   | _               | μΑ   |

### 2.4.2 Input Analog Levels (Remote Receivers)

| Parameter                     | Condition                                                      | Min  | Тур  | Max  | Unit |

|-------------------------------|----------------------------------------------------------------|------|------|------|------|

| Input Bias Voltage            | V <sub>cm</sub> = open,<br>R2K_EN = 1                          | 1.79 | 1.82 | 1.86 | V    |

|                               | $V_{cm} = 1.8V, V_{in} = \pm 100 \text{mV},$<br>$R2K_{EN} = 1$ |      | 4.2  |      | 10   |

| Differential Input Resistance | $V_{cm} = 1.8V, V_{in} = \pm 100 \text{mV}, R2K_EN = 0$        |      | 162  |      | kΩ   |

| ₿<br>}                        | V <sub>cm</sub> = 0V                                           | -7   |      | +7   | mV   |

| Input Voltage Offset          | V <sub>cm</sub> = 1.8V                                         | -5.5 |      | +5.5 | mV   |

|                               | V <sub>cm</sub> = V3P3A                                        | -7   |      | +5.1 | mV   |

2

2.4.3 Output Logic Levels

| Parameter                                         | Condition                 | Min            | Тур | Max | Unit |

|---------------------------------------------------|---------------------------|----------------|-----|-----|------|

|                                                   | I <sub>LOAD</sub> = 1mA   | V3P3D -<br>0.1 | -   | -   | v    |

| Digital high-level output voltage V <sub>он</sub> | I <sub>LOAD</sub> = 10mA  | V3P3D -<br>0.7 | -   | -   | v    |

|                                                   | I <sub>LOAD</sub> = -1mA  | 0              | _   | 0.1 | V    |

| Digital low-level output voltage Vo∟              | I <sub>LOAD</sub> = -10mA | -              | _   | 0.5 | V    |

| et oft                                            |                           |                |     |     |      |

### 2.4.4 Supply Current

| Parameter                                      | Condition                        | Min | Тур | Max  | Unit |

|------------------------------------------------|----------------------------------|-----|-----|------|------|

| V <sub>3P3D</sub> current                      | Normal Operation (all re-        | -   | 2.0 | 5.0  | mA   |

| V <sub>3P3A</sub> current                      | mote channels disabled)          | -   | 9.9 | 11.5 | mA   |

| Additional V <sub>3P3A</sub> Operating Current | Normal Operation (only           | 0   | 0.7 | 0.9  | mA   |

| Additional V <sub>3P3D</sub> Operating Current | one remote channel en-<br>abled) | 0   | 0.4 | 0.6  | mA   |

| Additional V <sub>3P3A</sub> Operating Current | Normal Operation (all re-        |     | 1.9 | 2.4  | mA   |

| Additional V <sub>3P3D</sub> Operating Current | mote channels enabled)           |     | 1.6 | 1.8  | mA   |

### 2.4.5 Internal RC Oscillator

| Parameter         | Condition         | Min 🖉 | Тур    | Max | Unit |

|-------------------|-------------------|-------|--------|-----|------|

| Nominal Frequency | V3P3 = 3.3V, 25ºC |       | 20.000 | -   | MHz  |

| Accuracy          |                   | -2    |        | +2  | %    |

$\binom{1}{0}$

### 2.4.6 External Crystal Oscillator

| Parameter                  | Condition                                       | Min  | Тур    | Max  | Unit |

|----------------------------|-------------------------------------------------|------|--------|------|------|

| Nominal Frequency          |                                                 | -    | 20.000 | _    | MHz  |

| Transconductance           | 4                                               | 1.3  | _      | _    | mS   |

| Peak Output Source Current | Startup with XIN = XOUT<br>= 0V, -40°C to +85°C | 950  |        | 1250 | μA   |

|                            | XIN = 1 peak, 20MHz                             | 0.58 |        | 1.45 | mA   |

| Timing Specifications      |                                                 |      |        |      |      |

|                            |                                                 |      |        |      |      |

#### Timing Specifications 2.5

2.5.1 SPI Slave Port

| Parameter                                                                                | Symbol | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|

| Setup time from fall of SSB to rise of SCK                                               | Tssu   | 10  |     |     | ns   |

| Setup time for SDI to rise of SCK                                                        | Tsu    | 10  |     |     | ns   |

| Hold time for SDI to rise of SCK                                                         | Thd    | 10  |     |     | ns   |

| Delay of SDO from fall of SCK                                                            | Td     |     |     | 40  | ns   |

| Hold time from rise of SCK to rise of SSB                                                | Tshd   | 15  |     |     | ns   |

| Period of SCK                                                                            | Tper   | 100 |     |     | ns   |

| Duration of SCK high state                                                               | Thi    | 50  |     |     | ns   |

| Duration of SCK low state                                                                | Tlo    | 50  |     |     | ns   |

| Bus Idle (Free) time between transactions<br>(time from rise of SSB to next fall of SSB) | Tbuf   | 250 |     |     | ns   |

### **2.6** Reset Specifications

### 2.6.1 Power-On Reset Voltage Thresholds

| Parameter               | Condition                                | Min  | Тур | Max  | Unit |

|-------------------------|------------------------------------------|------|-----|------|------|

| POR Release Threshold   | V3P3A rising until reset is released     | 0    |     | 1.76 | V    |

| POR Assertion Threshold | V3P3A falling until reset is<br>asserted | 1.56 |     | , e? | •    |

### 2.6.2 Transient Spike Tolerance

| Parameter                  | Condition            | Min | тур | Max  | Unit |

|----------------------------|----------------------|-----|-----|------|------|

| RESETB Tspike <sup>†</sup> | Negative going Spike | 300 | 600 | 1050 | ns   |

<sup>+</sup> When RESETB is asserted low, it must be held low at least Tspike (MAX) duration to assert a reset. Pulses narrower than Tspike (MIN) will be ignored.

### 2.7 Flash Memory Specifications

| Parameter                      | Condition                                                                                                       | 🗸 Min  | Тур | Max | Unit   |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|-----|-----|--------|

| Write Cycles Endurance         |                                                                                                                 | 20,000 |     |     | Cycles |

| Data Retention                 | ¶ <sub>A</sub> = 25°C                                                                                           | 100    |     |     | Years  |

| Data Retention                 | $T_A = 85^{\circ}C$                                                                                             | 25     |     |     | Years  |

| Page Erase Time                | Y                                                                                                               | 4      |     | 6   | ms     |

| Mass Erase Time                | The second se | 20     |     | 40  | ms     |

| Write Time (Word Program Time) | A A                                                                                                             | 6      |     | 7.5 | μs     |

Note 1: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: The device is not guaranteed to function outside its operating conditions.

Note 3: Production testing is performed at 25°C; limits at -40°C to +85°C are guaranteed by design, test or statistical correlation.

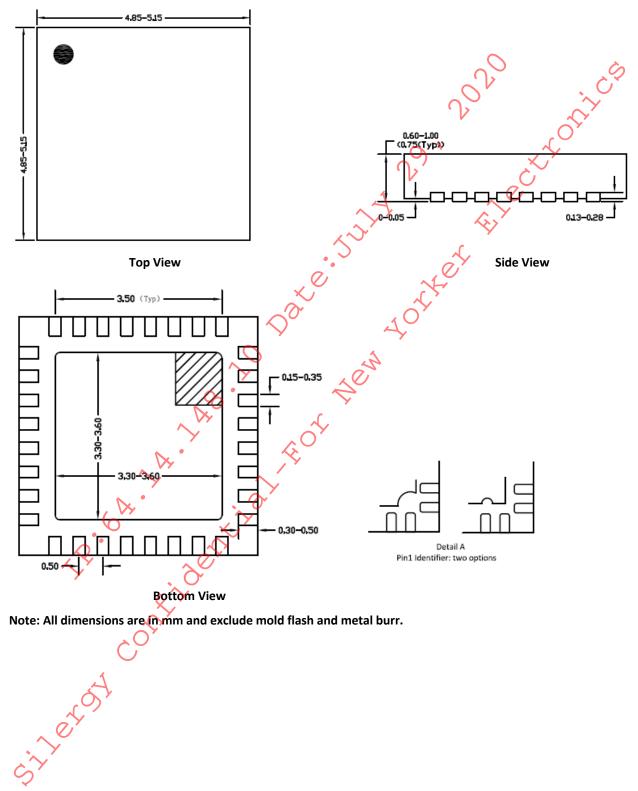

# 3 Mechanical Dimensions, PCB Layout, and Packaging Information

## 3.1 Mechanical Dimensions

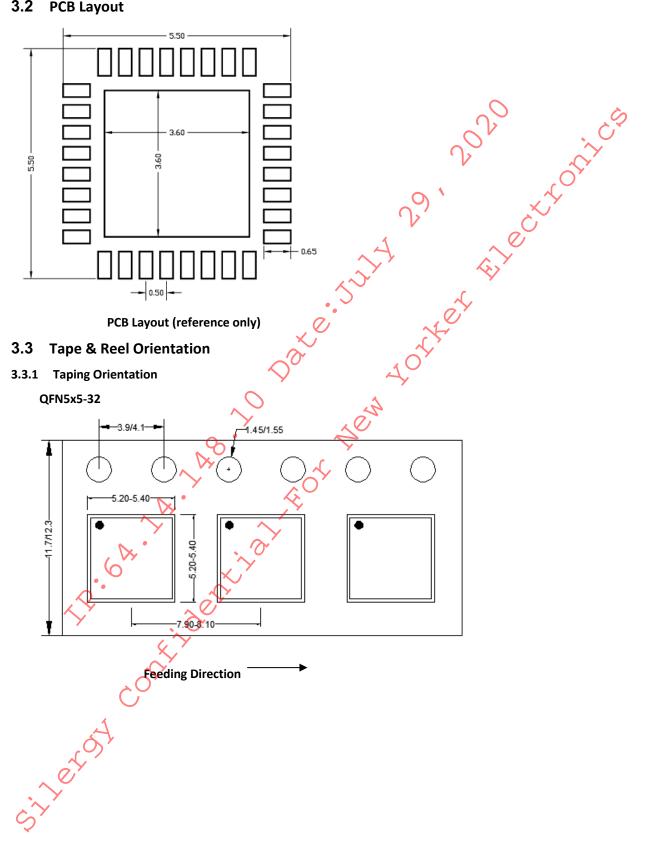

# 3.2 PCB Layout

### 3.3.2 Carrier Tape & Reel Specification for Packages

| Package type |

|--------------|

| QFN5x5-32    |

| QFN5x5-32    |

### **Revision History**

| 0.9 |

|-----|

| 0.5 |

|     |

|     |

|     |

### **IMPORTANT NOTICE**

1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, montor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

3. Limited warranty and liability. Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

5. **Terms and conditions of commercial sale**. Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

6. No offer to sell or license. Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

© 2020 Silergy Corp.

All Rights Reserved.